Timing simulation

2017-07-31 22:15Я наконец осилил back annotation в Верилоге. Это когда синтезируется прошивка для Xilinx FPGA, и на этапе, когда уже известно точное расположение всех элементарных примитивов, образуется файл с описанием всех задержек для каждого провода и логического вентиля. Даже есть такой стандартный формат SDF, или Standard Delay Format. После этого синтезированная схема преобразуется обратно в Верилог (структурный) и симулируется, загружая SDF-файл как набор параметров тайминга. Предполагается, что временная диаграмма такой симуляции будет примерно соответствовать реальному железу.

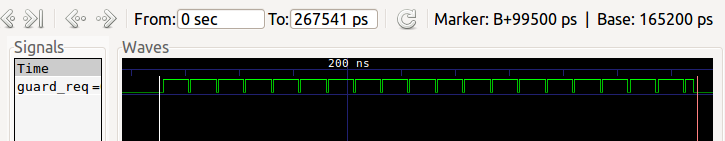

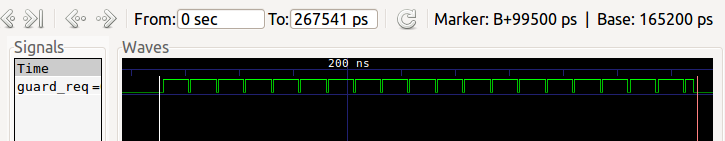

Вот что я получил для упомянутого сигнала цикла вычисления наибольшего общего делителя. Цикл в 20 итераций должет выполняться за 99500 пикосекунд, или почти ровно 100 нсек.

В реальности на осциллографе имеем 500 нсек.

Как-то точность времянки не особо радует. Плюс-минус порядок получается.

Вот что я получил для упомянутого сигнала цикла вычисления наибольшего общего делителя. Цикл в 20 итераций должет выполняться за 99500 пикосекунд, или почти ровно 100 нсек.

В реальности на осциллографе имеем 500 нсек.

Как-то точность времянки не особо радует. Плюс-минус порядок получается.