GateMate PC

2026-01-01 18:36Теперь и Европа делает свои микросхемы FPGA. Вот прелестная платка от фирмы Olimex с чипом GateMate от немецкой фирмы Cologne Chip.

Документация на FPGA: ds1001-gatemate1-datasheet-latest.pdf

Бибилиотека примитивов: ug1001-gatemate1-primitives-library-latest.pdf

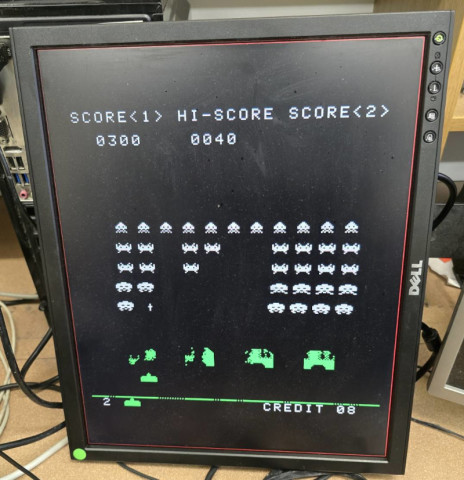

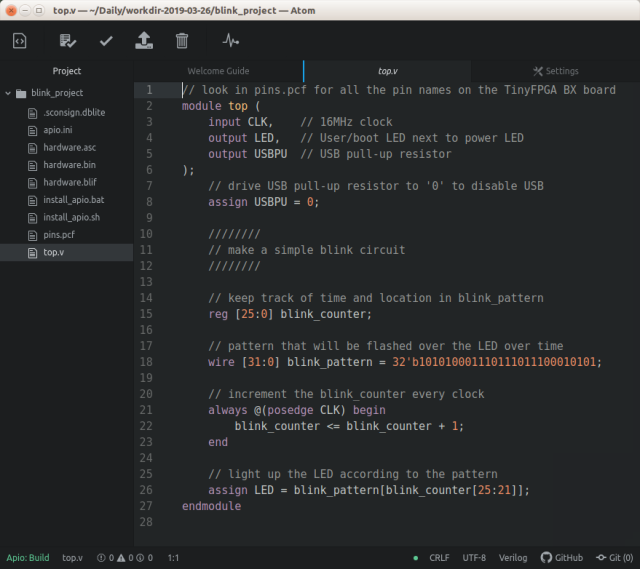

Из интересных примеров для этой платы есть известная игра Space Invaders: gitlab.com/x653/spaceinvaders-fpga

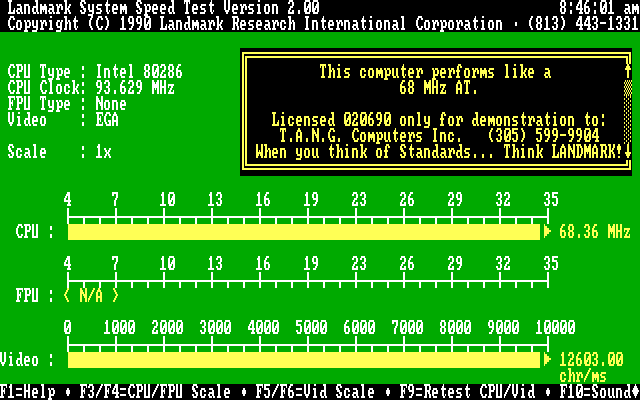

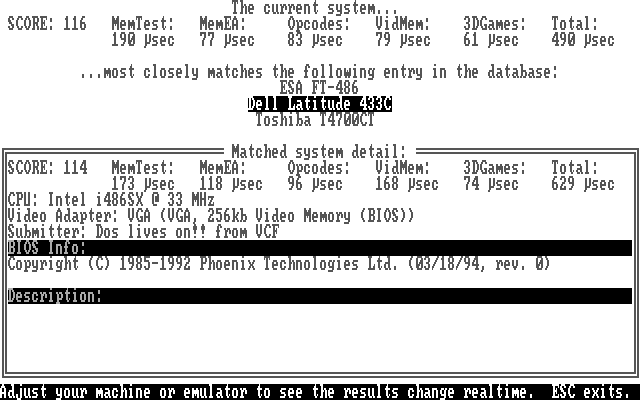

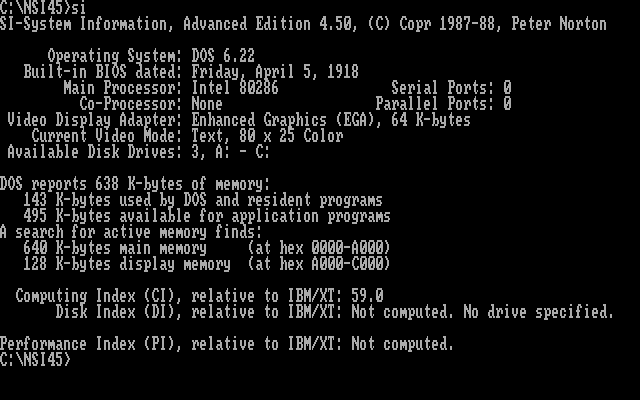

![[personal profile]](https://www.dreamwidth.org/img/silk/identity/user.png) ymz5 ведёт проект персонального компьютера RISC-V на основе этой платы: gitlab.com/gatemate/pc

ymz5 ведёт проект персонального компьютера RISC-V на основе этой платы: gitlab.com/gatemate/pc

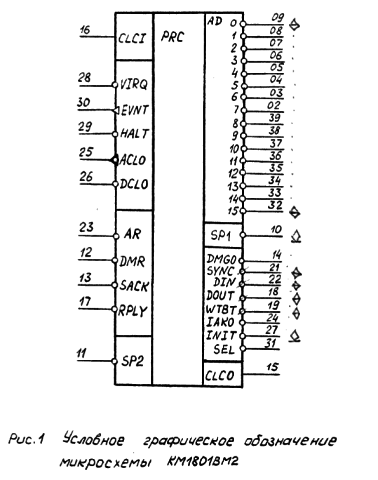

Я вот думаю, может имеет смысл и мэсм-6 сюда портонуть?

Документация на FPGA: ds1001-gatemate1-datasheet-latest.pdf

Бибилиотека примитивов: ug1001-gatemate1-primitives-library-latest.pdf

Из интересных примеров для этой платы есть известная игра Space Invaders: gitlab.com/x653/spaceinvaders-fpga

Я вот думаю, может имеет смысл и мэсм-6 сюда портонуть?